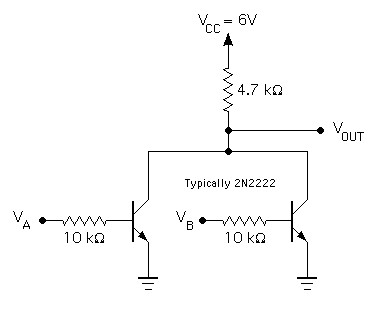

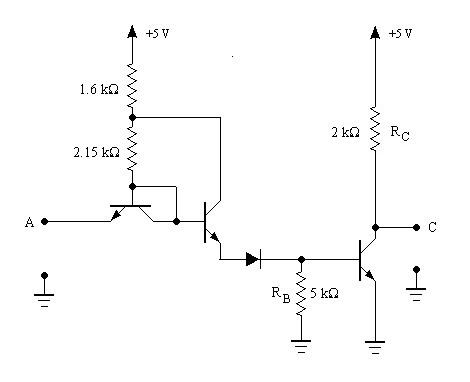

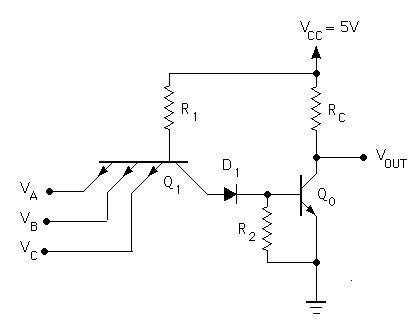

Low to High

Transistion

- The time required to discharge the Q1 depletion layers is

<< 1ns.

- The time required to extract the Q2 base charge is also

<< 1ns:

- Q1 becomes forward active;

- IBR becomes large for Q2

- Removal of base charge from QO is similar to the DTL

case. With R2 = 1 kW,

ts = 10ns (typical values for 7400 series TTL).

|

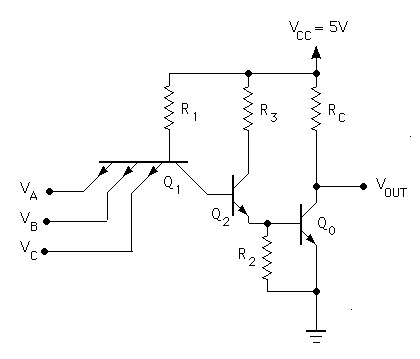

High to Low

Transistion

- The depletion capacitance of the Q1 EB junction must

discharge;

- Base charge must be removed from the saturated Q2

- Ditto for QO

- The capactive load must be charged to VCC.

|